For more than 50 years, computer chip designers have primarily used one tactic to improve performance: They shrunk electronic components to put more force on each piece of silicon.

More than a decade ago, engineers at the chipmaker Advanced Micro Devices started playing with a radical idea. Instead of designing one large microprocessor with huge numbers of tiny transistors, they envisioned making one of smaller chips that would be tightly packed together to act as one electronic brain.

The concept, known as chiplets, was a huge success with AMD, Apple, Amazon, Tesla, IBM and Intel introducing such products. Chiplets quickly gained traction because smaller chips are cheaper to make, while bundles of them can exceed the performance of any piece of silicon.

The strategy, based on advanced packaging technology, has since become an essential tool in enabling progress in semiconductors. And it represents one of the biggest shifts in years for an industry driving innovation in areas like artificial intelligence, self-driving cars and military hardware.

“Packaging is where the action will be,” said Subramanian Iyer, a professor of electrical and computer engineering at the University of California, Los Angeles, who helped pioneer the chiplet concept. “It happens because there really is no other way.”

The catch is that such packaging, like making your own chips, is overwhelmingly dominated by companies in Asia. Although the United States accounts for about 12 percent of global semiconductor production, U.S. companies supply only 3 percent of chip packages, according to IPC, an industry association.

That issue has now brought chiplets into the center of US industrial policymaking. The CHIPS Act, a $52 billion grant package passed last summer, was seen as President Biden’s move to revive domestic chip production by providing funds to build more advanced plants that will become “factories.” named. But part of it was also to kick-start state-of-the-art packaging plants across the United States to capture more of that vital process.

“As chips get smaller, the way you arrange the chips, which is the packaging, becomes more and more important and that’s what we need to do in America,” Commerce Secretary Gina Raimondo said in a speech at Georgetown University in February.

The Department of Commerce is now accepting applications for production grants from the CHIPS Act, including for chip packaging factories. It also awards funding to a research program specifically in the field of advanced packaging.

Some chip packaging companies are moving quickly for funding. One is Integra Technologies in Wichita, Kan., which announced plans for a $1.8 billion expansion there but said it was contingent on receiving federal grants. Amkor Technology, an Arizona-based packaging service that has most of its operations in Asia, also said it was talking to customers and government officials about a U.S. manufacturing presence.

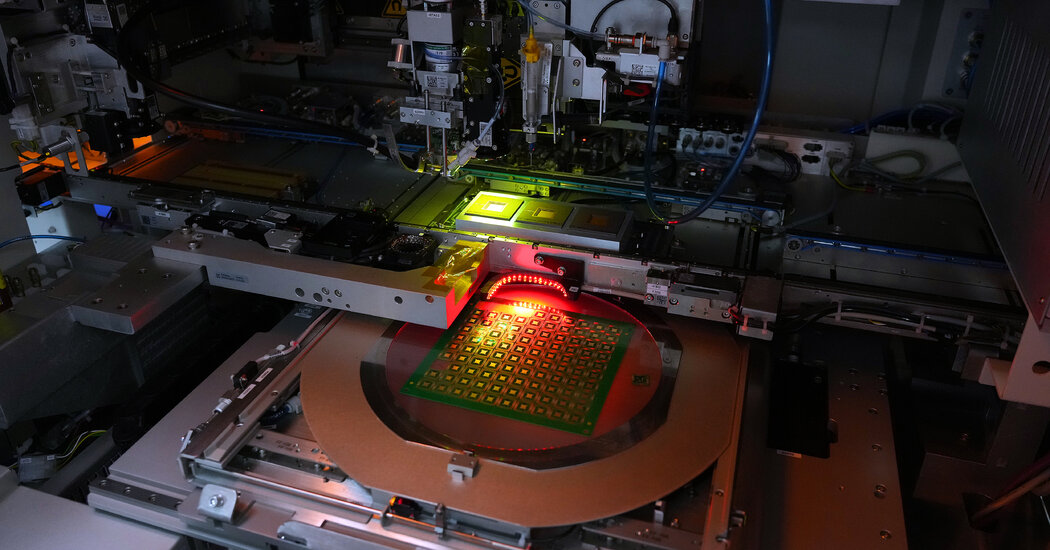

Packing chips together isn’t a new concept, and chiplets are just the latest iteration of that idea, using advances in technology that help cram the chips closer together — side-by-side or stacked on top of each other — along with faster electrical connections between them.

“What’s unique about chiplets is the way they’re electrically connected,” said Richard Otte, the CEO of Promex Industries, a chip packaging service in Santa Clara, California.

Chips can’t do anything without some way to connect them to other components, which means they need to be placed in some kind of package that can transmit electrical signals. That process begins after factories complete the first phase of production, which can create hundreds of chips on a silicon wafer. Once that wafer is sliced apart, individual chips are usually bonded to an important base layer called a substrate, which can conduct electrical signals.

That combination is then coated with protective plastic, forming a package that can be connected to a printed circuit board that is essential for connection to other components in a system.

These processes originally required a lot of manual work, which led Silicon Valley companies to move their packaging to low-wage countries in Asia more than 50 years ago. Most chips are flown to packaging services in countries such as Taiwan, Malaysia, South Korea and China.

Since then, packaging developments have gained in importance due to diminishing returns from Moore’s Law, the shorthand for chip miniaturization that has driven progress in Silicon Valley for decades. It’s named after Gordon Moore, a co-founder of Intel whose 1965 paper described how quickly companies doubled the number of transistors on a typical chip, improving performance at a lower cost.

But these days, smaller transistors aren’t necessarily cheaper, in part because building factories for advanced chips can cost $10 billion to $20 billion. Large, complex chips are also expensive to design and often have more manufacturing defects, even though companies in fields like generative AI want more transistors than can currently be packed into the largest chip manufacturing machines.

“The natural response to that is to pack more stuff into a package,” said Anirudh Devgan, CEO of Cadence Design Systems, whose software is used to design both conventional chips and chiplet-like products.

Synopsys, a rival, said it tracked more than 140 customer projects based on packaging multiple chips together. According to the market research firm Yole Group, as many as 80 percent of microprocessors will use chiplet-style designs by 2027.

Today, companies typically design all chiplets in a package along with their own connection technology. But industry groups are working on technical standards to make it easier for companies to assemble products from chiplets that come from different manufacturers.

The new technology is now mainly used for extreme performance. Intel recently introduced a processor called Ponte Vecchio with 47 chiplets that will be used in a powerful supercomputer at Argonne National Laboratory, near Chicago.

In January, AMD announced plans for an unusual product, the MI300, which combines standard computation chiplets with others designed for computer graphics, along with a large inventory of memory chips. That processor, intended to power another advanced supercomputer at Lawrence Livermore National Laboratory, has 146 billion transistors, compared to tens of billions for the most advanced conventional chips.

Sam Naffziger, a senior vice president of AMD, said it was no easy feat for the company to deploy its server computer chip business on chiplets. The complexity of the packaging was a major hurdle, he said, which was eventually overcome with help from an unnamed partner.

But chiplets paid off for AMD. According to Mercury Research, the company has sold more than 12 million chips based on the idea since 2017 and has become a major player in the microprocessors powering the internet.

Packaging services still need others to provide the substrates that chiplets need to connect to printed circuit boards and each other. One of the companies driving the chiplet boom is Taiwan Semiconductor Manufacturing Company, which already makes chips for AMD and hundreds of others and offers an advanced silicon-based substrate called an interposer.

Intel has developed similar technology and improved on cheaper conventional plastic substrates, in an approach favored by some, such as Silicon Valley start-up Eliyan. Intel has also developed new packaging prototypes under a Pentagon program and hopes to receive CHIPs Act support for a new pilot packaging plant.

But the United States has no major makers of those substrates, which are mainly produced in Asia and stem from technologies used in manufacturing printed circuit boards. Many U.S. companies have also exited that business, another concern that industry groups hope will boost federal funding to help cardboard suppliers make substrates.

In March, Mr. Biden determined that advanced packaging and household circuit board manufacturing were essential to national security, and announced $50 million in Defense Production Act funding for U.S. and Canadian companies in those fields.

Even with such grants, it is “a formidable challenge” to gather all the elements needed to reduce U.S. reliance on Asian companies,” said Andreas Olofsson, who led a Department of Defense research effort in the field before launching a packaging launch. -up called Zero ASIC. “You have no suppliers. You have no workforce. You have no equipment. You have to kind of start from scratch.”

Anne Swanson reporting contributed.